ethomaz said:

|

HoloDust said:

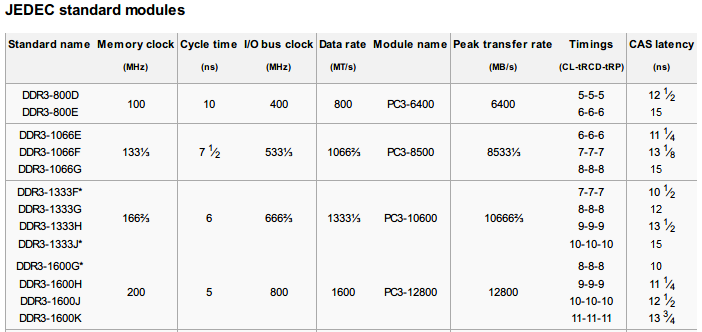

Not sure he did - 800MHz * 2bytes (16bits) * 4 modules = 6.4GByte/s.

I think you calculated in Gbits: 800MHz * 16bit = 12.8Gbits/s (*4 modules = 51.2Gbits/s = 6.4GBytes/s)

I might be wrong though, not completely sure if this is correct calculus.

|

I think the right maths is...

800Mhz (the clock) * 2 (bits/line, DDR have 2) * 16bits (bus width) * 4 (modules) = 102,400 Mbits/s = 12,800 MBytes/s = 12.8 GByte/s

|

Here is even better math (curiously it's even the correct math since it is directly from Samsung's spec sheet for the chips) :

Data Speed/Pin 2,133 Mbps

Bandwidth/Chip 4.266 GB/s

Burst Length 4, 8

For four chips, this gives you 17Gbytes/s (for 8 cycles = 10ns at 800MHz)