Trumpstyle said:

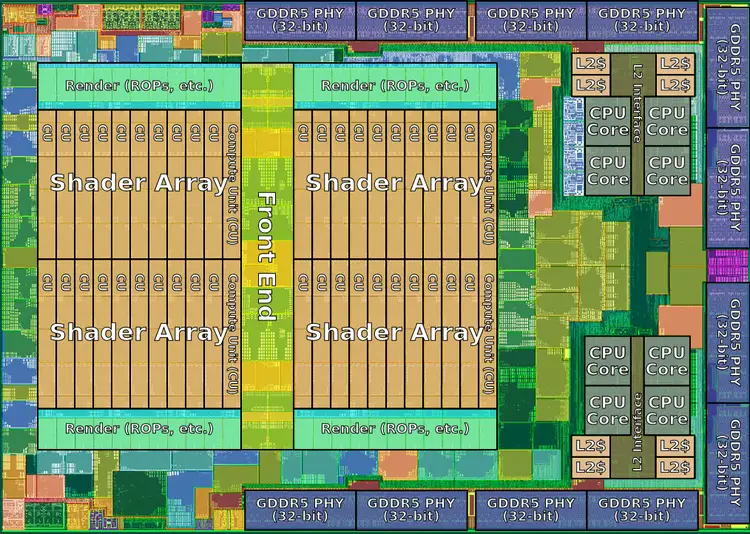

The GPU (Navi10) already has a I/O die, there's no need for another one. As for the CPU, 2x zen2 CCX are 70mm2, you cut off 24mb of the GameCache it should land around 40mm2, and I think the devkit has all 64CU's activated so Microsoft will simply disable 4/8 CU's and up the clock-speed to hit 12TF. There's no 72CU's. Wasted die area, what I mean by that is you can't pack everything into a perfect Square/rectangle, here's a die shot of Xbox one X:

Even though we can't see the I/O stuff, you can see the CU's, the 32-bit controllers and the 2 CPU clusters aren't packed into a perfect Square/rectangle that's what I mean by wasted die area. You will always have wasted die area. Edit: Forgot about double chip, Microsoft has already shown a monolith die in there E3 video, it will be a APU/SOC. |

Often you have areas of "Dark Silicon" in order to reduce leakage.

You also often have extra functional units in order to increase yields incase part of the chip is non-functional.

Some parts of a chip are also duplicated on other parts of the chip because it works out to be cheaper than actually putting in the routing.

There are lots of considerations that go into chip design.

About 40-50mm without the caches seems very plausible for Zen2 chiplets.

www.youtube.com/@Pemalite